News

Testonica's services support Estonian Chip Competence Center

With a 50 billion allocation under the European Chips Act, each EU country is poised to enhance its efforts in securing a position within the semiconductor value chain. Being fully integrated into the...Read More

With a 50 billion allocation under the European Chips Act, each EU country is poised to enhance its efforts in securing a position within the semiconductor value chain. Being fully integrated into the...Read MoreTestonica launched Newsletter on LinkedIn

If you are not following Testonica on LinkedIn yet, then it is the right time to do it here as now there is also an opportunity to subscribe to Newsletter.

...Read More

If you are not following Testonica on LinkedIn yet, then it is the right time to do it here as now there is also an opportunity to subscribe to Newsletter.

...Read MoreMeet Testonica at The Winter Satellite Workshop 2024 in Helsinki

The Winter Satellite Workshop running this week near Helsinki, Finland is definitely the place to be for a space professional or an enthusiast - reports Artur Jutman, CEO of Testonica. With over 1000 ...Read More

The Winter Satellite Workshop running this week near Helsinki, Finland is definitely the place to be for a space professional or an enthusiast - reports Artur Jutman, CEO of Testonica. With over 1000 ...Read MoreTestonica at Space Tech Expo Europe 2023

"Space Tech Expo Europe 2023 is running full-speed and the two first days were full of technical conversations and new business contacts" - reports Dr. Artur Jutman, CEO of Testonica.

He adds that "t...Read More

"Space Tech Expo Europe 2023 is running full-speed and the two first days were full of technical conversations and new business contacts" - reports Dr. Artur Jutman, CEO of Testonica.

He adds that "t...Read MoreThe productronica 2023 is on

We are excited to take part in productronica 2023 in Munich! If you would like to ask any details about our Quick Instruments or discuss partnering opportunities firsthand, then you can meet our Produ...Read More

We are excited to take part in productronica 2023 in Munich! If you would like to ask any details about our Quick Instruments or discuss partnering opportunities firsthand, then you can meet our Produ...Read MoreMeet Testonica at productronica 2023

Come and join us in Messe München hall B2.344 at the upcoming productronica 2023 fair. We will present our latest products, test and programming solutions.

Testonica has 15+ years of experience de...Read More

Come and join us in Messe München hall B2.344 at the upcoming productronica 2023 fair. We will present our latest products, test and programming solutions.

Testonica has 15+ years of experience de...Read MoreTestonica featured on Tessent Silicon Lifestyle Solutions' YouTube channel

The Tessent Silicon Lifestyle Solutions has recently posted the video about Testonica`s projects, where an FPGA board hosted a replica of IEEE Std. 1687 compliant scan networks and embedded instrument...Read More

The Tessent Silicon Lifestyle Solutions has recently posted the video about Testonica`s projects, where an FPGA board hosted a replica of IEEE Std. 1687 compliant scan networks and embedded instrument...Read MoreForesight Centre: Testonica has capacity and expertise needed to benefit from global demand towards IC development services

The Foresight Centre at the Parliament of Estonia has mentioned Testonica among a few Estonian companies having capacity and expertise needed to benefit from increasing global demand towards IC develo...Read More

The Foresight Centre at the Parliament of Estonia has mentioned Testonica among a few Estonian companies having capacity and expertise needed to benefit from increasing global demand towards IC develo...Read MoreTestonica CEO elected as a Council Member at Estonian Electronics Industries Association

Testonica CEO, Artur Jutman has been just elected to serve as a Council Member at Estonian Electronics Industries Association (EETL). The Council comprises of 12 members elected for the period of two ...Read More

Testonica CEO, Artur Jutman has been just elected to serve as a Council Member at Estonian Electronics Industries Association (EETL). The Council comprises of 12 members elected for the period of two ...Read MoreTestonica CEO speaks at CERN`s High-Level Delegation visit

Testonica CEO gave a talk today for CERN's High-Level Delegation visiting Estonia May 22-24 with the purpose to evaluate the country's readiness to fulfill the full membership criteria. Artur Jutman r...Read More

Testonica CEO gave a talk today for CERN's High-Level Delegation visiting Estonia May 22-24 with the purpose to evaluate the country's readiness to fulfill the full membership criteria. Artur Jutman r...Read MoreTestonica received a Certificate of Recognition from Advantest

Testonica has just received a Certificate of Recognition from Advantest for our work presented at VOICE 2023 Developer Conference (VOICE 2023) which took place last week in Santa Clara, USA. The prese...Read More

Testonica has just received a Certificate of Recognition from Advantest for our work presented at VOICE 2023 Developer Conference (VOICE 2023) which took place last week in Santa Clara, USA. The prese...Read MoreTestonica's presentation at Siemens's EDA User2User Conference

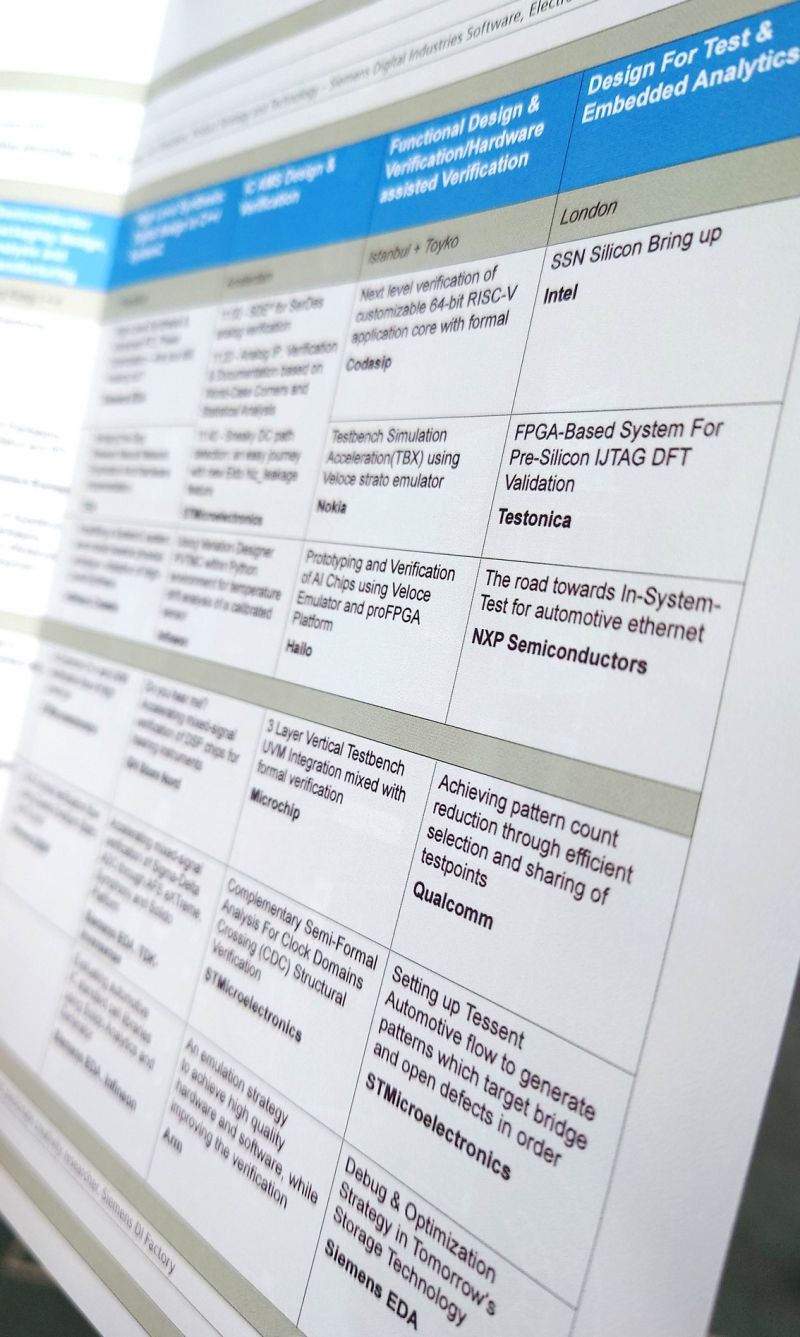

Testonica`s CEO Artur Jutman speaks at Siemens's EDA User2User Europe 2023 conference in Munich about pre-silicon IJTAG and SW tool ecosystem co-validation sharing experience and lessons learned in tw...Read More

Testonica`s CEO Artur Jutman speaks at Siemens's EDA User2User Europe 2023 conference in Munich about pre-silicon IJTAG and SW tool ecosystem co-validation sharing experience and lessons learned in tw...Read MoreTestonica is a sponsor of the the 26th DDECS

R&D and deep tech are in the heart and in the guts of Testonica's team since the beginning of our story in 2005. Therefore, we are proud to be contributing by sponsorship and assistance in organiz...Read More

R&D and deep tech are in the heart and in the guts of Testonica's team since the beginning of our story in 2005. Therefore, we are proud to be contributing by sponsorship and assistance in organiz...Read MoreMeet us at Embedded World 2023

Embedded World 2023 – one of the world's leading trade shows for the international embedded community will take place next week - March 14–16 in the Nürnberg Messe, Nuremberg, Germany.

...Read More

Embedded World 2023 – one of the world's leading trade shows for the international embedded community will take place next week - March 14–16 in the Nürnberg Messe, Nuremberg, Germany.

...Read MoreFulitech Technology Co., Ltd. Joins the Quick Instruments Team for China mainland

Testonica keeps on its expansion to Asia and now there is Chinese mainland distribution partner Fulitech Technology Co., Ltd, located in Shenzhen. Fulitech will provide integration services and techni...Read More

Testonica keeps on its expansion to Asia and now there is Chinese mainland distribution partner Fulitech Technology Co., Ltd, located in Shenzhen. Fulitech will provide integration services and techni...Read MoreTestonica takes part in Big Science Business Forum 2022

Testonica participates as a part of the Estonian delegation at BSBF2022 - Big Science Business Forum 2022. Come by to the Estonian booth (83-84) and talk to Testonica's Artur Jutman about life and tec...Read More

Testonica participates as a part of the Estonian delegation at BSBF2022 - Big Science Business Forum 2022. Come by to the Estonian booth (83-84) and talk to Testonica's Artur Jutman about life and tec...Read MoreTestonica exhibits at electronica 2022 in Munich

Come visit us November 15-18th at the electronica 2022 trade fair in Munich where we demonstrate our Quick Instruments technology portfolio. You are welcome to see us at Hall B1, stand no 413.

...Read More

Come visit us November 15-18th at the electronica 2022 trade fair in Munich where we demonstrate our Quick Instruments technology portfolio. You are welcome to see us at Hall B1, stand no 413.

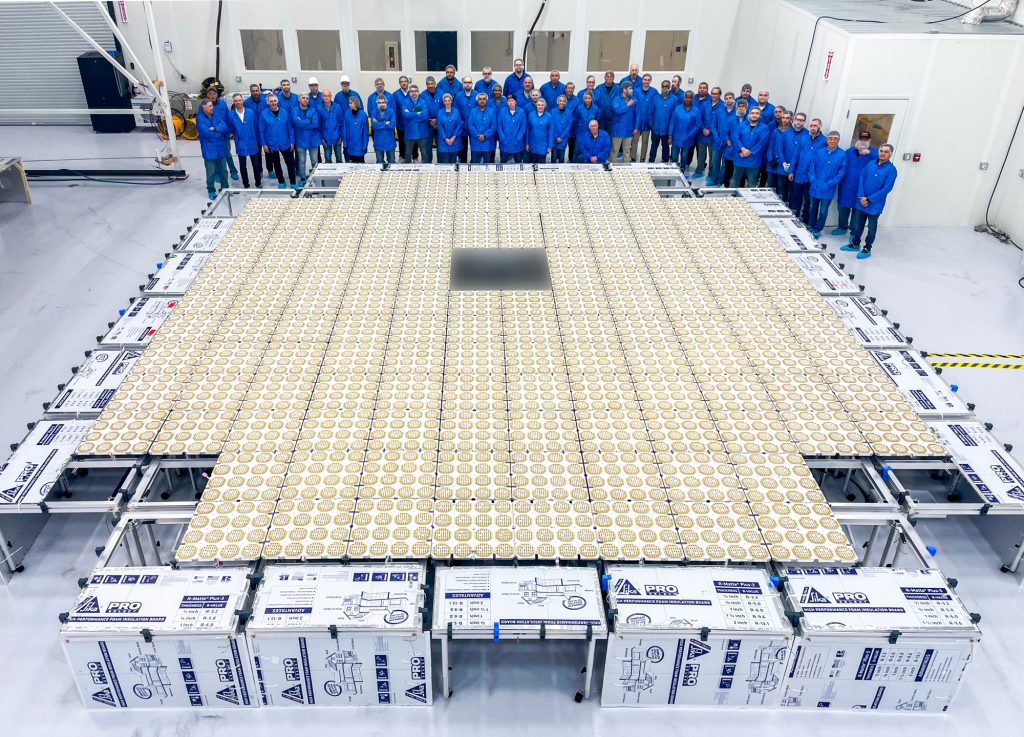

...Read MoreTestonica helped to build the test setup for a low Earth orbiting sattellite

Testonica is celebrating the AST SpaceMobile's success! We helped the AST team to build the test setup for the BlueWalker 3 electronics and were very happy to learn that the satellite is alive in orbi...Read More

Testonica is celebrating the AST SpaceMobile's success! We helped the AST team to build the test setup for the BlueWalker 3 electronics and were very happy to learn that the satellite is alive in orbi...Read MoreTestonica signed a Memorandum of Understanding with the CERN

Testonica CEO, Artur Jutman signed today a Memorandum of Understanding with the CERN's Future Circular Collider Study (FCC) division. The focus of the MoU is the technical and financial feasibility st...Read More

Testonica CEO, Artur Jutman signed today a Memorandum of Understanding with the CERN's Future Circular Collider Study (FCC) division. The focus of the MoU is the technical and financial feasibility st...Read MoreTestonica's presentation at Workshop on European Silicon Lifecycle Management (eSLM)

Testonica's CEO, Artur Jutman shares today his view on functional safety perspective w.r.t. system degradation pointing out to the need for adaptive safety mechanisms taking into account system's wear...Read More

Testonica's CEO, Artur Jutman shares today his view on functional safety perspective w.r.t. system degradation pointing out to the need for adaptive safety mechanisms taking into account system's wear...Read More