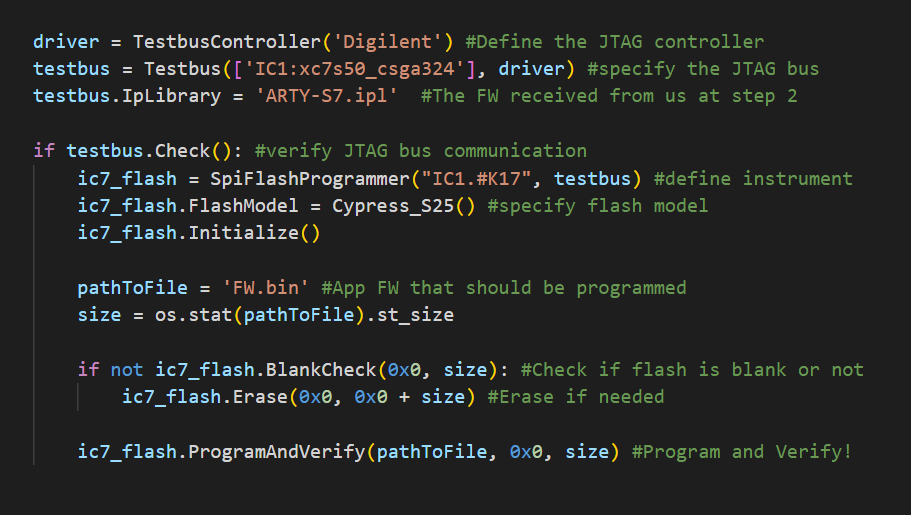

Configuration Flash Programming Options at Production Floor

Technology* | IP Loading | Program | Verify | Performance |

|---|---|---|---|---|

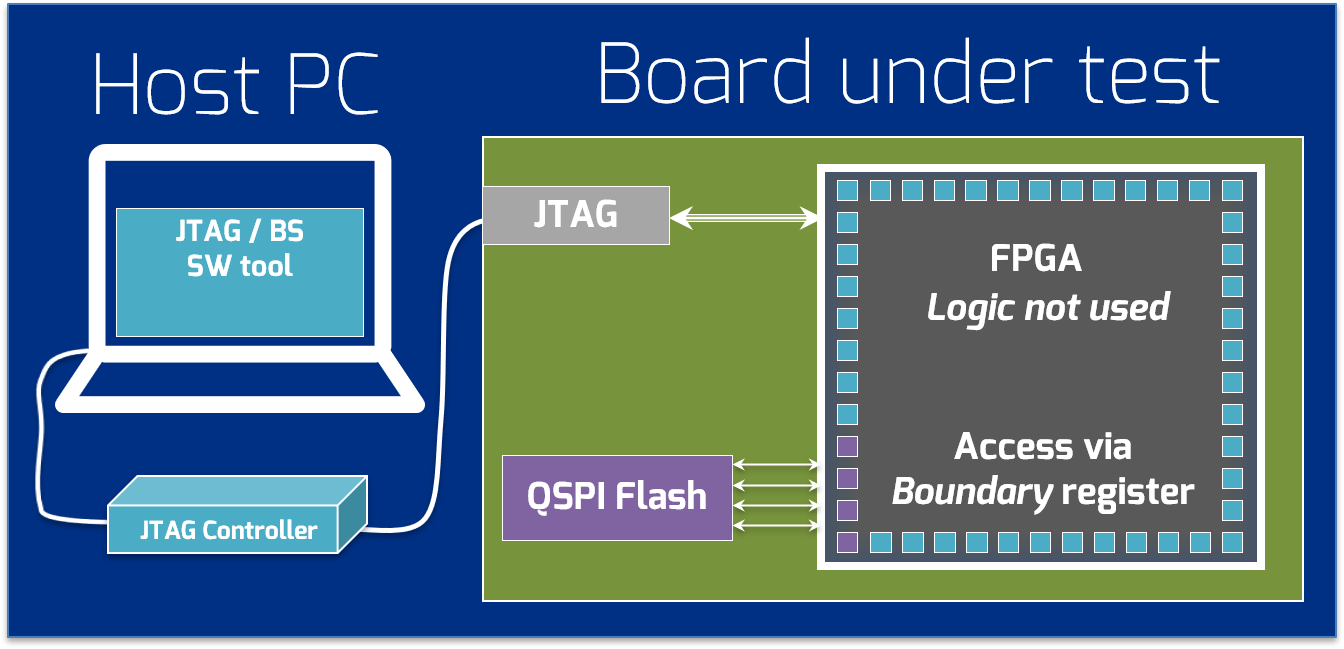

Boundary Scan | ----- | 11m 31s | 17m 44s | 0.0065 Mbps |

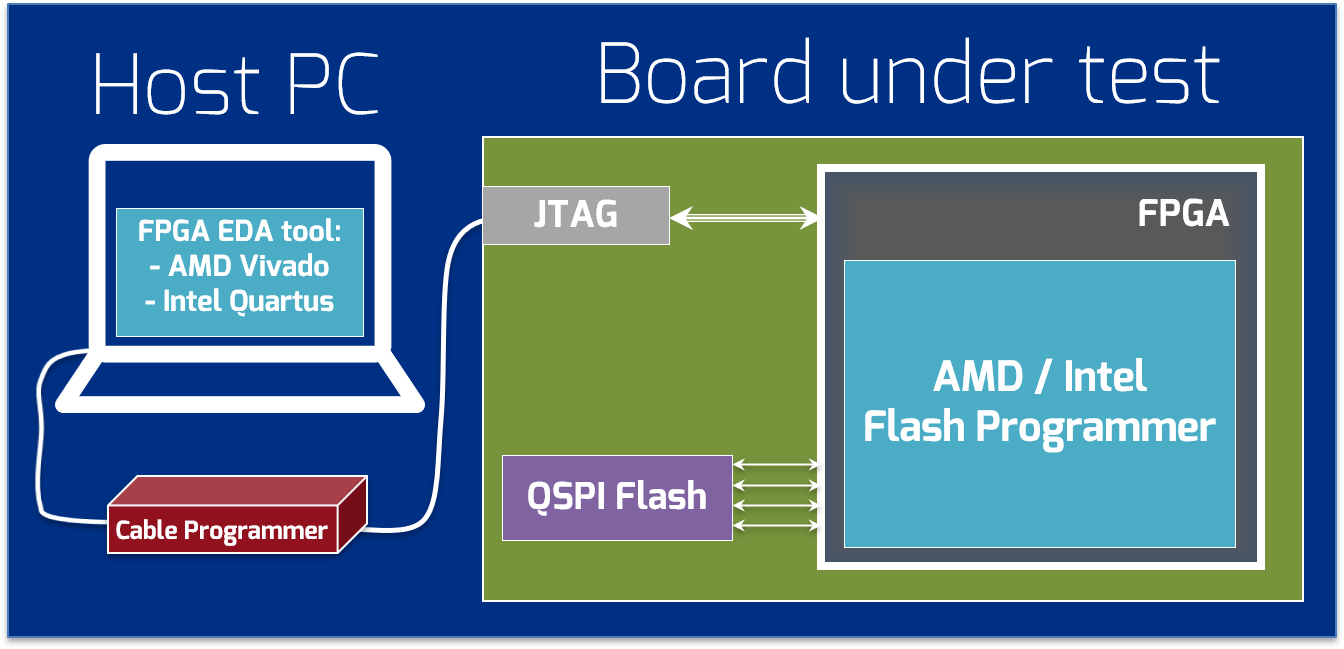

AMD Vivado Programmer | 1.0 s | 25.6 s | 4.3 s | 0.37 Mbps |

Göpel's ChipVORX | 1.0 s | 2.5 s | 2.0 s | 2.06 Mbps |

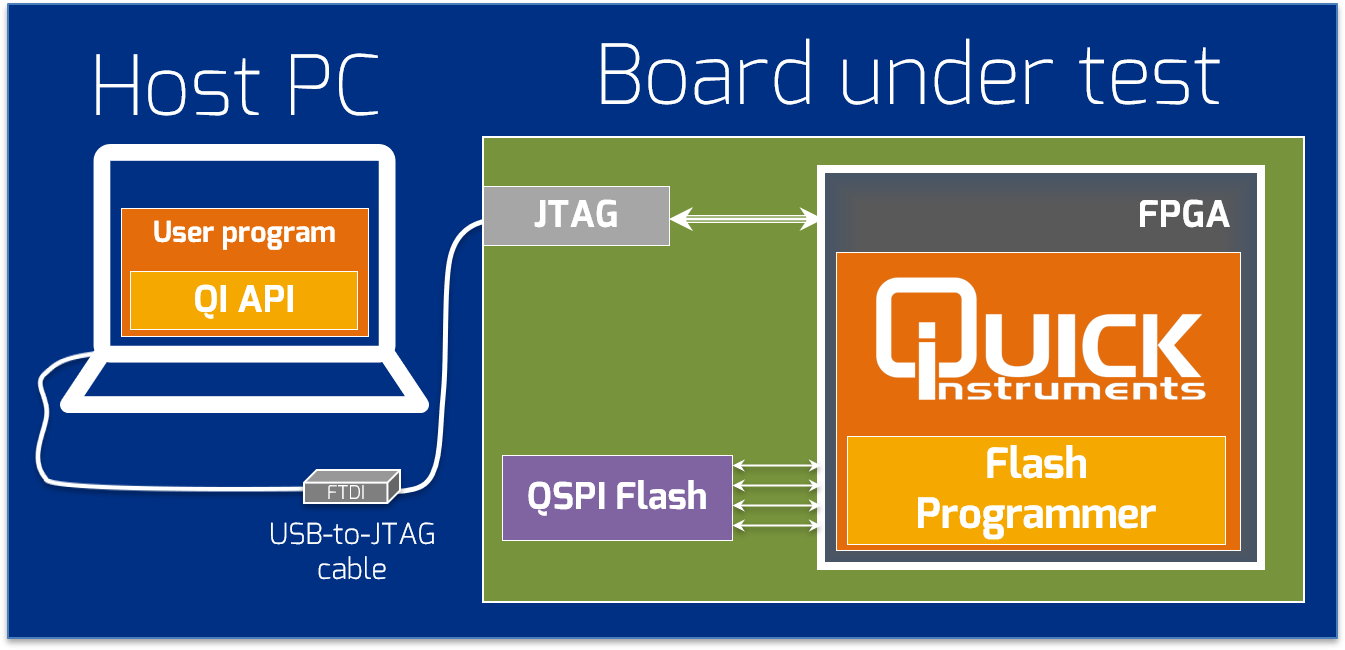

QI Flash Programmer | 1.0 s | 4.0 s | 0.05 s | 2.25 Mbps |

*JTAG TCK speed was set to 30MHz in all casesAs expected, Boundary Scan was the slowest technology for programming. It took almost half an hour to program a relatively small firmware image. Vivado was 57x faster than BS but still, it showed a modest (although exactly as expected) result. This programming speed is enough for the prototype validation phase but as AMD itself claims "it is not intended for high-volume production programming". Göpel's ChipVORX demonstrated very good performance and taking into consideration that this technology comes off-the-shelf (no FPGA EDA tools required, the FPGA instrument is supplied with their SW) has a very promising fit-for-function performance.