Testonica delivers embedded Bit-Error Rate Test (BERT) technology

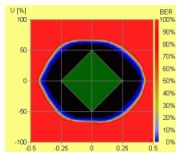

The delivered solution enables quality evaluation of up to 10Gbit serial buses (PCIe Gen1/2/3, SATA, optical fiber channel, etc) with a help of powerful FPGA-embedded instrumentation technology. The technology is capable to measure Bit-Error Rate (BER) characteristic for high-speed digital data transmission links as well as to plot so-called BER eye diagram. The latter feature directly fits for mass-production testing since allows every manufactured product to be quickly checked for potential problems on high-speed channels.

Embedded BER tester is JTAG-controlled and supports adjustment of various transmission parameters such drive strength, pre-emphasis, equalization settings. Simultaneous testing of multiple serial channels is also supported which is necessary for screening out possible crosstalk issues. Unlike traditional link quality measurement equipment embedded BER instrument IP does not require physical invasion (a nail probe) and does not bring problems of signal distortion: the measurement is taken from inside of FPGA exactly in the same way as in real-life mode of operation.

The first release that supports Xilinx Virtex6 and Kintex7 FPGA families would be later extended with support of Xilinx 7-Series FPGAs as well as Altera StratixIV and ArriaV devices.