Testonica's presentation at Siemens's EDA User2User Conference

Testonica`s CEO Artur Jutman speaks at Siemens's EDA User2User Europe 2023 conference in Munich about pre-silicon IJTAG and SW tool ecosystem co-validation sharing experience and lessons learned in two recently completed projects where an FPGA board hosted a replica of IEEE Std. 1687 compliant scan networks and embedded instrumentation in a way that fully resembles a final in-silicon implementation.

The reasons for such a HW/SW co-validation could be numerous. Here are a few examples:

- evaluate performance of embedded instrumentation and in-system monitoring facilities

- evaluate scan-network performance, e.g. in different topological implementations

- check correctness of ICL descriptions and top-level PDLs against the HW implementation

- evaluate SW tools to be used to control instruments in-field or in production

- validate on the fly retargeting and instrument handling

- evaluate security and safety features of IJTAG infrastructure by emulating attacks

- demonstrate different features of the integrated HW/SW tool ecosystem.

In both case studies, the IJTAG network implemented inside the reconfigurable logic of an FPGA has multiple layers of hierarchy and arranges the instruments into several sub-networks of various interconnection topologies. The network provides read/write access to internal registers (some general-purpose, some property checkers e.g. in ALU, registers, pipeline, program counter and some built-in resources such as on-chip temperature and voltage sensors) as well as outwards-oriented instruments connected to external LEDs and switches on the board.

The two case studies were performed in collaboration with Advantest and ESA/ESTEC respectively.

The latter one was aimed at instant in-system fault detection (or functional property violation detection) directly within the logic with subsequent recovery in OS/SW while in mission-mode operation. The measurements demonstrated worst case fault detection latency of 3 TCKs i.e. 74ns and the overall fault handling latency in SW in the order of milliseconds. The in-system monitoring demonstrator handles over 1200 embedded instruments simultaneously in real time.

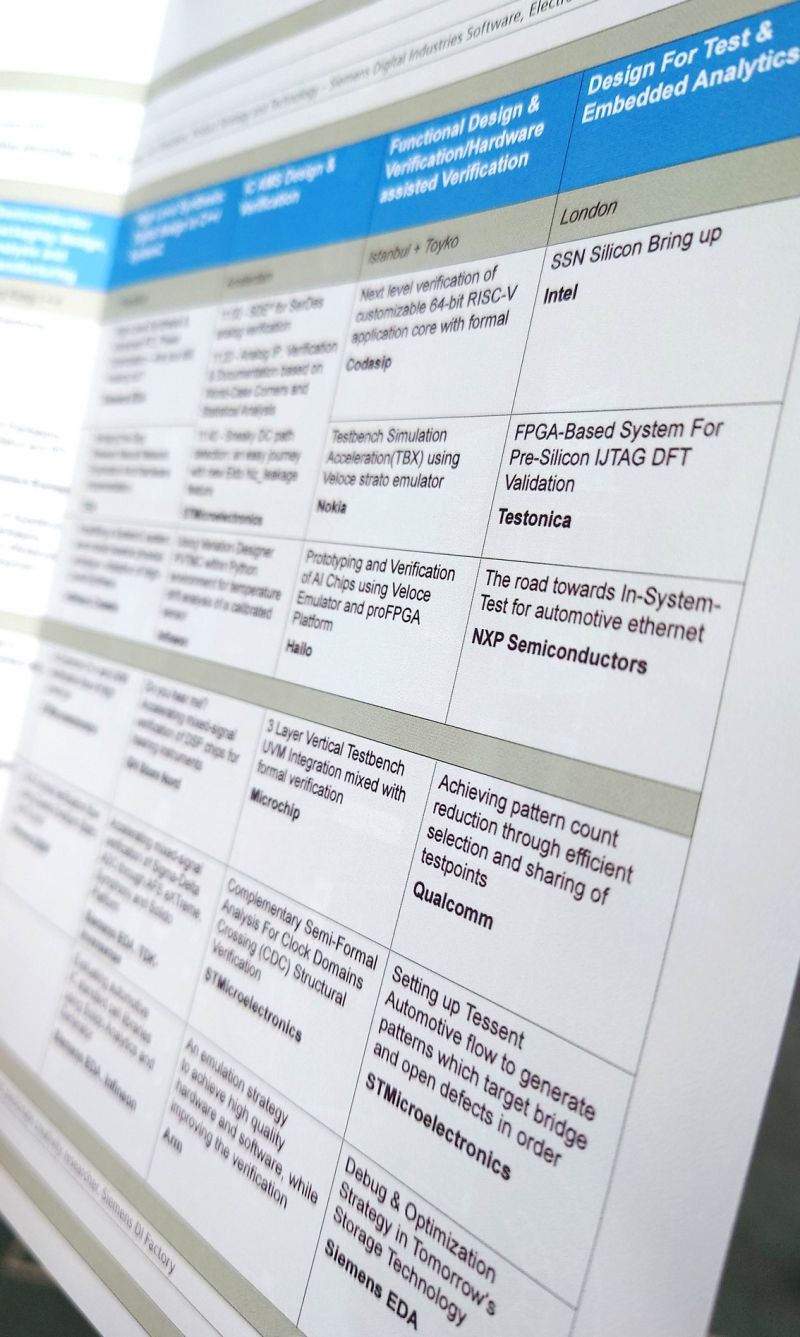

The presentation is part of the Design for Test (DFT) and Embedded Analytics track of Siemens's EDA User2User Conference.

Other presenters in the DFT track are:

Ofri Brenroth, Intel Corporation

Arjen Bakker, NXP Semiconductors

Sanmati Jain, Qualcomm

Fatma Messaoudi and Simon Ribeyron, STMicroelectronics

Hanan Moller, Siemens EDA.

The event was organized by Siemens EDA (Siemens Digital Industries Software) and attended by approx. 300 professionals from the sector of microelectronics in a broad sense. Testonica thanks organizers for an excellent event and extremely welcoming approach to attendees and speakers. Special thanks to Lee Harrison, Sil Singh and Denis Lobzov.